主要概念

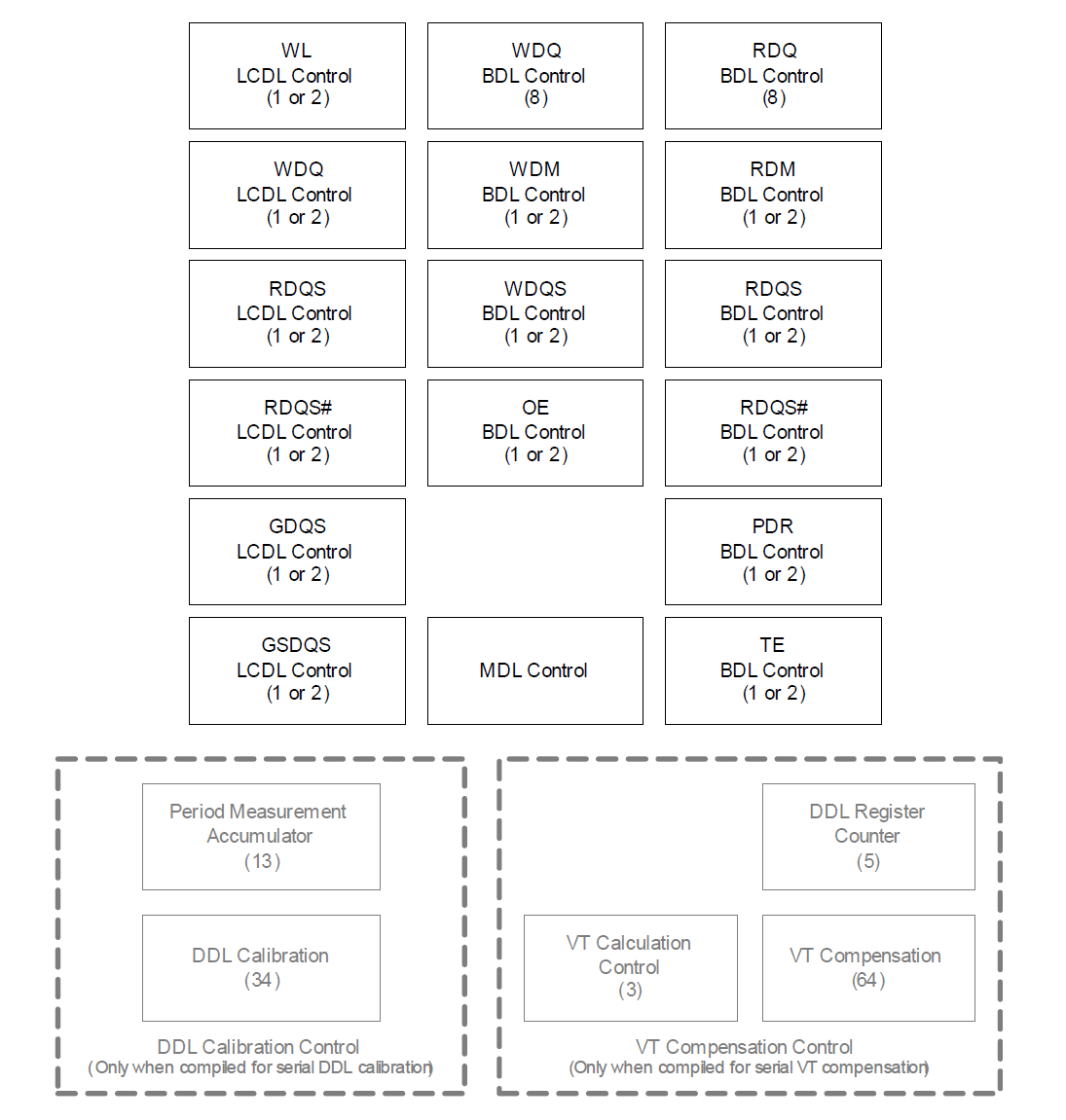

1. LCDL的类型

- 每个字节通道有6种类型的LCDL:

- WL LCDL(写入均衡LCDL):用于平衡写入信号。

- WDQ LCDL(写数据LCDL):用于控制写入数据。

- GDQS LCDL(读DQS门LCDL):用于读取DQS信号的门控。

- RDQS LCDL(读DQS LCDL):用于读取DQS信号。

- RDQS# LCDL(读DQS# LCDL):DQS的反向信号。

- GSQDS LCDL(读DQS门状态LCDL):用于监测DQS门的状态。

- 每种LCDL都有相应的控制逻辑,具体的控制逻辑在后文提到。

2. x4支持:

- 对于x4模式,每个字节通道有两个LCDL控制逻辑实例,以独立控制两个半字节(nibble)。

3. MDL控制逻辑:

- 每个字节通道还包括一个MDL控制逻辑实例,用于控制主延迟线(MDL)。

4. BDL控制逻辑:

- 每个字节还包括多个BDL控制逻辑实例,用于独立控制每个字节通道的BDL。

- 写路径BDL

- 包括8个写数据(WDQ)BDL、1个(或2个,适用于x4)写数据掩码(WDM)BDL、1个(或2个,适用于x4)写数据时钟(WDQS)BDL、1个(或2个,适用于x4)输出使能(OE)BDL。

- 读路径BDL

- 包括8个读数据(RDQ)BDL、1个(或2个,适用于x4)读数据掩码(RDM)BDL、1个(或2个,适用于x4)读数据时钟(RDQS)BDL、1个(或2个,适用于x4)读数据时钟#(RDQS#)BDL、1个(或2个,适用于x4)功耗下降接收器(PDR)BDL和1个(或2个,适用于x4)终端使能(TE)BDL。

5. DDL控制的校准和VT补偿:

- 字节通道的DDL控制具有将DDL校准和VT补偿串行进行的选项,而不是并行进行。

- 这种选项允许将DDL校准和VT补偿逻辑实例化一次,而不是在每个LCDL控制块中重复该逻辑。

- 但串行校准和VT补偿的缺点是操作时间会增加。

总结

这段文字的主要内容是介绍了每个字节通道中的LCDL和BDL的控制逻辑、如何进行独立控制以及在x4模式下的扩展。此外,它还提到DDL控制的校准和VT补偿可以选择串行或并行执行,这对于设计的复杂性和操作时间都有影响。

本文作者:

ICXNM-ZLin

本文链接: https://talent-tudou.github.io/2024/10/28/DDR/Data Byte DDL Control/

版权声明: 本作品采用 CC BY-NC-SA 4.0 进行许可。转载请注明出处!

本文链接: https://talent-tudou.github.io/2024/10/28/DDR/Data Byte DDL Control/

版权声明: 本作品采用 CC BY-NC-SA 4.0 进行许可。转载请注明出处!